3-3.*Suppose that the A input in Figure 3-52 is unintentionally shorted to the 5 V supply line (i.e., A 1). Draw the resulting output waveform.

3-4. Read the statements below concerning an OR gate.At first, they may appear to be valid,but after some thought you should realize that neither one is alwaystrue.Prove this by showing a specific example to refute each statement. (a) If the output waveform from an OR gate is the same as the waveform at one of its inputs, the other input is being held permanently LOW. (b) If the output waveform from an OR gate is always HIGH,one of its inputs is being held permanently HIGH.

3-5. How many different sets of input conditions will produce a HIGH output from a five-input OR gate?

3-6. Change the OR gate in Figure 3-52 to an AND gate. (a)*Draw the output waveform. (b) Draw the output waveform if the A input is permanently shorted to ground. (c) Draw the output waveform if A is permanently shorted to 5 V.

3-7.*Refer to Figure 3-4. Modify the circuit so that the alarm is to be activated only when the pressure and the temperature exceed their maximum limits at the same time.

3-8.*Change the OR gate in Figure 3-6 to an AND gate and draw the output waveform.

3-9. Suppose that you have an unknown two-input gate that is either an OR gate or an AND gate.What combination of input levels should you apply to the gate’s inputs to determine which type of gate it is?

3-10. True or false: No matter how many inputs it has, an AND gate will produce a HIGH output for only one combination of input levels.

3-11. Apply the A waveform from Figure 3-23to the input of an INVERTER. Draw the output waveform. Repeat for waveform B.

3-12. (a)* Write the Boolean expression for output x in Figure 3-53(a). Determine the value of x for all possible input conditions, and list the values in a truth table. (b) Repeat for the circuit in Figure 3-53(b).

3-13.*Create a complete analysis table for the circuit of Figure 3-15(b) by finding the logic levels present at each gate output for each of the 32 possible input combinations.

3-14. (a)*Change each OR to an AND, and each AND to an OR, in Figure 3-15(b).Then write the expression for the output. (b) Complete an analysis table.

3-15. Create a complete analysis table for the circuit of Figure 3-16 by finding the logic levels present at each gate output for each of the 16 possible combinations of input levels.

3-16. For each of the following expressions, construct the corresponding logic circuit, using AND and OR gates and INVERTERs.

3-17. *(a) Apply the input waveforms of Figure 3-54to a NOR gate,and draw the output waveform. (b) Repeat with C held permanently LOW. (c) Repeat with C held HIGH.

3-18. Repeat Problem 3-17 for a NAND gate.

3-19.*Write the expression for the output of Figure 3-55, and use it to determine the complete truth table.Then apply the waveforms of Figure 3-54 to the circuit inputs, and draw the resulting output waveform.

3-21. Modify the circuits that were constructed in Problem 3-16 so that NAND gates and NOR gates are used wherever appropriate.

3-22. Prove theorems (15a) and (15b) by trying all possible cases.

3-23.*DRILL QUESTION Complete each expression.

3-24. (a)*Simplify the following expression using theorems (13b),(3),and (4):

(b) Simplify the following expression using theorems (13a),(8),and (6):

3-26. Simplify each of the following expressions using DeMorgan’s theorems

3-27.*Use DeMorgan’s theorems to simplify the expression for the output of Figure 3-55.

3-28. Convert the circuit of Figure 3-53(b) to one using only NAND gates. Then write the output expression for the new circuit,simplify it using DeMorgan’s theorems, and compare it with the expression for the original circuit.

3-29. Convert the circuit of Figure 3-53(a) to one using only NOR gates. Then write the expression for the new circuit, simplify it using DeMorgan’s theorems, and compare it with the expression for the original circuit.

3-30. Show how a two-input NAND gate can be constructed from two-input NOR gates.

3-31. Show how a two-input NOR gate can be constructed from two-input NAND gates.

3-32. A jet aircraft employs a system for monitoring the rpm, pressure, and temperature values of its engines using sensors that operate as follows:

RPM sensor output = 0 only when speed 6 4800 rpm

P sensor output = 0 only when pressure 6 220 psi

T sensor output = 0 only when temperature 6 200°F

Figure 3-56 shows the logic circuit that controls a cockpit warning light for certain combinations of engine conditions.Assume that a HIGH at output W activates the warning light. (a)*Determine what engine conditions will give a warning to the pilot. (b) Change this circuit to one using all NAND gates.

3-33. For each statement below, draw the appropriate logic-gate symbol— standard or alternate—for the given operation. (a) A HIGH output occurs only when all three inputs are LOW. (b) A LOW output occurs when any of the four inputs is LOW. (c) A LOW output occurs only when all eight inputs are HIGH.

3-34. Draw the standard representations for each of the basic logic gates. Then draw the alternate representations.

3-35. The circuit of Figure 3-55 is supposed to be a simple digital combination lock whose output will generate an active-LOW signal for only one combination of inputs. (a)*Modify the circuit diagram so that it represents more effectively the circuit operation. (b) Use the new circuit diagram to determine the input combination that will activate the output. Do this by working back from the output using the information given by the gate symbols, as was done in Examples 3-22 and 3-23. Compare the results with the truth table obtained in Problem 3-19.

3-36. (a) Determine the input conditions needed to activate output Z in Figure 3-37(b). Do this by working back from the output, as was done in Examples 3-22 and 3-23. (b) Assume that it is the LOW state of Z that is to activate the alarm. Change the circuit diagram to reflect this, and then use the revised diagram to determine the input conditions needed to activate the alarm.

3-37. Modify the circuit of Figure 3-40 so that A1 0 is needed to produce DRIVE 1 instead of A1= 1.

3-38.*Determine the input conditions needed to cause the output in Figure 3-57 to go to its active state.

3-40. Use the results of Problem 3-38 to obtain the complete truth table for the circuit of Figure 3-57.

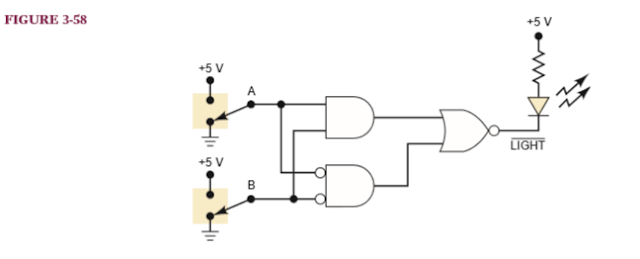

3-41.*Figure 3-58 shows an application of logic gates that simulates a twoway switch like the ones used in our homes to turn a light on or off from two different switches. Here the light is an LED that will be ON (conducting) when the NOR gate output is LOW.Note that this output is labeled to indicate that it is active-LOW. Determine the input conditions needed to turn on the LED.Then verify that the circuit operates as a two-way switch using switches A and B. (In Chapter 4, you will learn how to design circuits like this one to produce a given relationship between inputs and outputs.)

3-42. Redraw the circuits of (a)* Figure 3-57 and (b) Figure 3-58 using the IEEE/ANSI symbols.

3-43.*True or false: (a) VHDL is a computer programming language. (b) VHDL can accomplish the same thing as AHDL. (c) AHDL is an IEEE standard language. (d) Each intersection in a switch matrix can be programmed as an open or short circuit between a row and column wire. (e) The first item that appears at the top of an HDL listing is the functional description. (f) The type of an object indicates if it is an input or an output. (g) The mode of an object determines if it is an input or an output. (h) Buried nodes are nodes that have been deleted and will never be used again. (i) Local signals are another name for intermediate variables. (j) The header is a block of comments that document vital information about the project.

3-44. Redraw the programmable connection matrix from Figure 3-44.Label the output signals (horizontal lines) from the connection matrix (from top row to bottom row) as follows: AAABADHE. Draw an X in the appropriate intersections to short-circuit a row to a column and create these connections to the logic circuit.

Get 3.44 exercise solution

3-45.*Write the HDL code in the language of your choice that will produce the following output functions:

X = A+ B

Y= AB

Z= A+ B+ C

3-46. Write the HDL code in the language of your choice that will implement the logic circuit of Figure 3-39. (a) Use a single Boolean equation. (b) Use the intermediate variables V, W, X, and Y.

3-47.*Refer to Figure 3-40 in Example 3-23.Inputs A7 through A0 are address inputs that are supplied to this circuit from outputs of the microprocessor chip in a microcomputer.The eight-bit address code A7 to A0 selects which device the microprocessor wants to activate.In Example 3-23, the required address code to activate the disk drive was A7 through A0 = 111111102 = FE16. Modify the circuit so that the microprocessor must supply an address code of 4A16 to activate the disk drive.

3-48. Show how can be implemented with one two-input NOR and one two-input NAND gate.

3-49.*Implement y ABCD using only two-input NAND gates.